Want to know exactly how VCs evaluate your chips startup?

Together with Intel Capital—one of the leading chips VCs—we’ve built this guide to unpack the inside baseball on how VCs evaluate chips startups, and in turn how you can raise a successful round.

Informed by reviewing thousands of decks, and insights on which startups get the most traction on Deep Checks, this playbook helps put together a teaser deck that gets your first VC pitch scheduled.

We’ll go slide by slide on how investors decide whether or not to move forward with a startup. It’ll cover:

- Problem: Demonstrating you're solving a burning pain point for your customers

- Solution: Show why you have the best solution to this problem

- Technical risk: How to convince investors to get behind the remaining technical risk that you have

- Traction: How to show there's demand for your product before the market has adopted it

- Why now?: Demonstrating why your startup has just become possible to build. This is make-or-break for many pitches

- Business Model: How VCs think about your economics

- Market Size: Why bottom up beats top down

- Go to market: Showing you can become big enough, fast enough

- Competition: As markets become crowded, how to create defensibility

- Team: What makes for a world-class founding team?

- The Ask: Use of proceeds and round size

- Pitching: Do's and dont's of pitching your startup to VCs

Problem

Demonstrating you're solving a burning pain point for your customers

The problem slide exists to convince VCs the pain point you’re solving for your customers is a large, distinct, burning issue that they are willing to endure switching costs to solve.

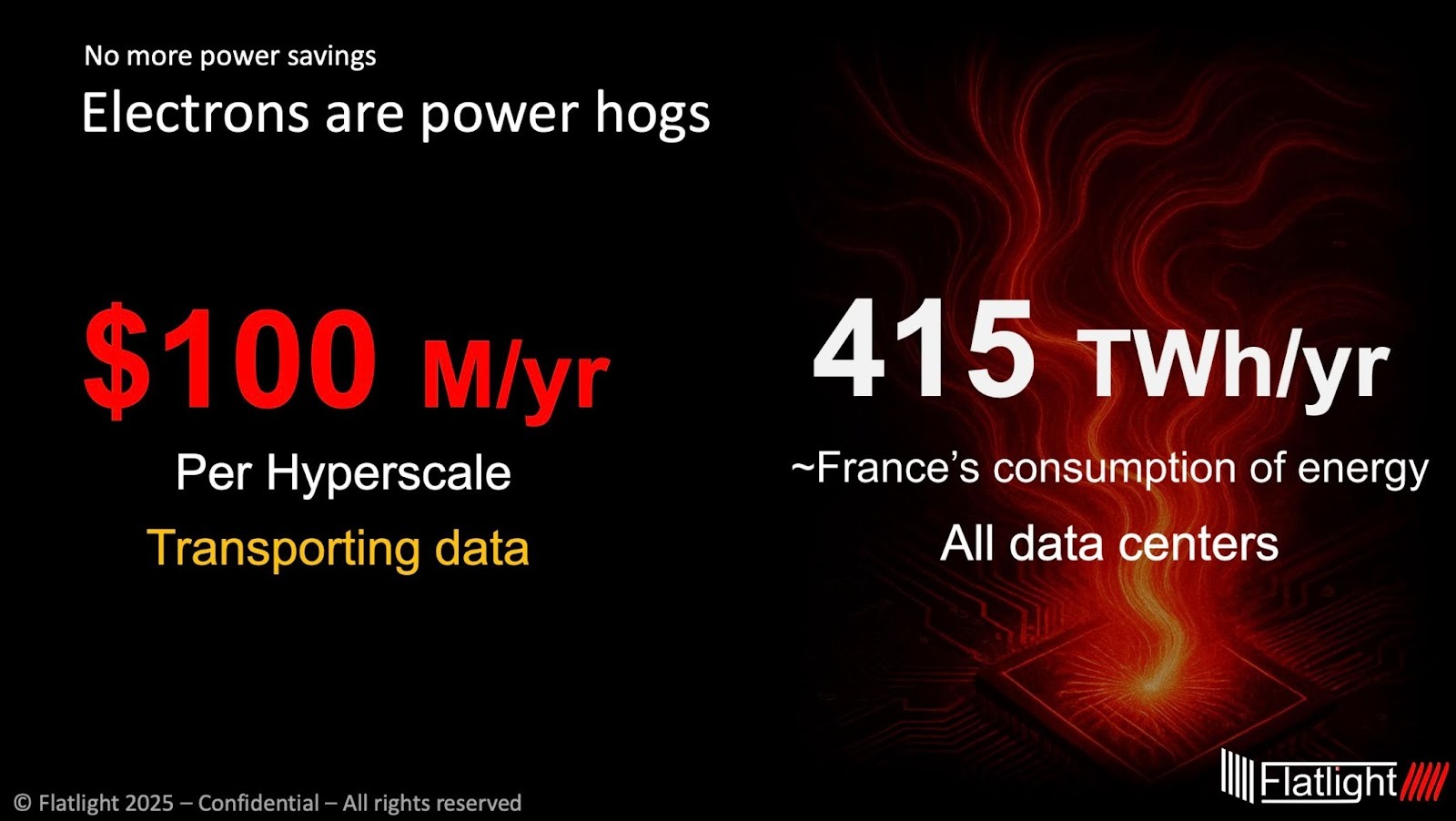

Semiconductor problems typically fall into one of four categories: compute performance/efficiency limitations, manufacturing and supply chain constraints, power consumption barriers, or market access and cost pressures. The most compelling chips pitches quantify the operational pain point with specific metrics:

- Compute bottlenecks: AI training clusters spending $50M+ annually on electricity alone, data centers hitting thermal limits that cap GPU density, or inference workloads requiring 10x more efficiency to be economically viable at the edge

- Supply chain dependencies: 18-24 month lead times for advanced node capacity, 92% concentration of leading-edge logic in Taiwan, or single-source dependencies on critical EDA tools or IP blocks

- Power/efficiency gaps: Mobile devices constrained to 5W thermal envelopes, automotive chips requiring operation from -40°C to 150°C, or IoT sensors needing to run for 10 years on a coin cell battery

- Cost barriers: Tapeout costs exceeding $100M at 3nm, mask sets running $15M+ at 5nm, or EDA tool licenses costing $500K+ annually per seat—pricing out all but the largest players

Frame the problem in terms of customer outcomes, not technology gaps. Instead of "current architectures can't scale," show "our hyperscaler customer loses $30M annually in stranded compute due to memory bandwidth limitations."

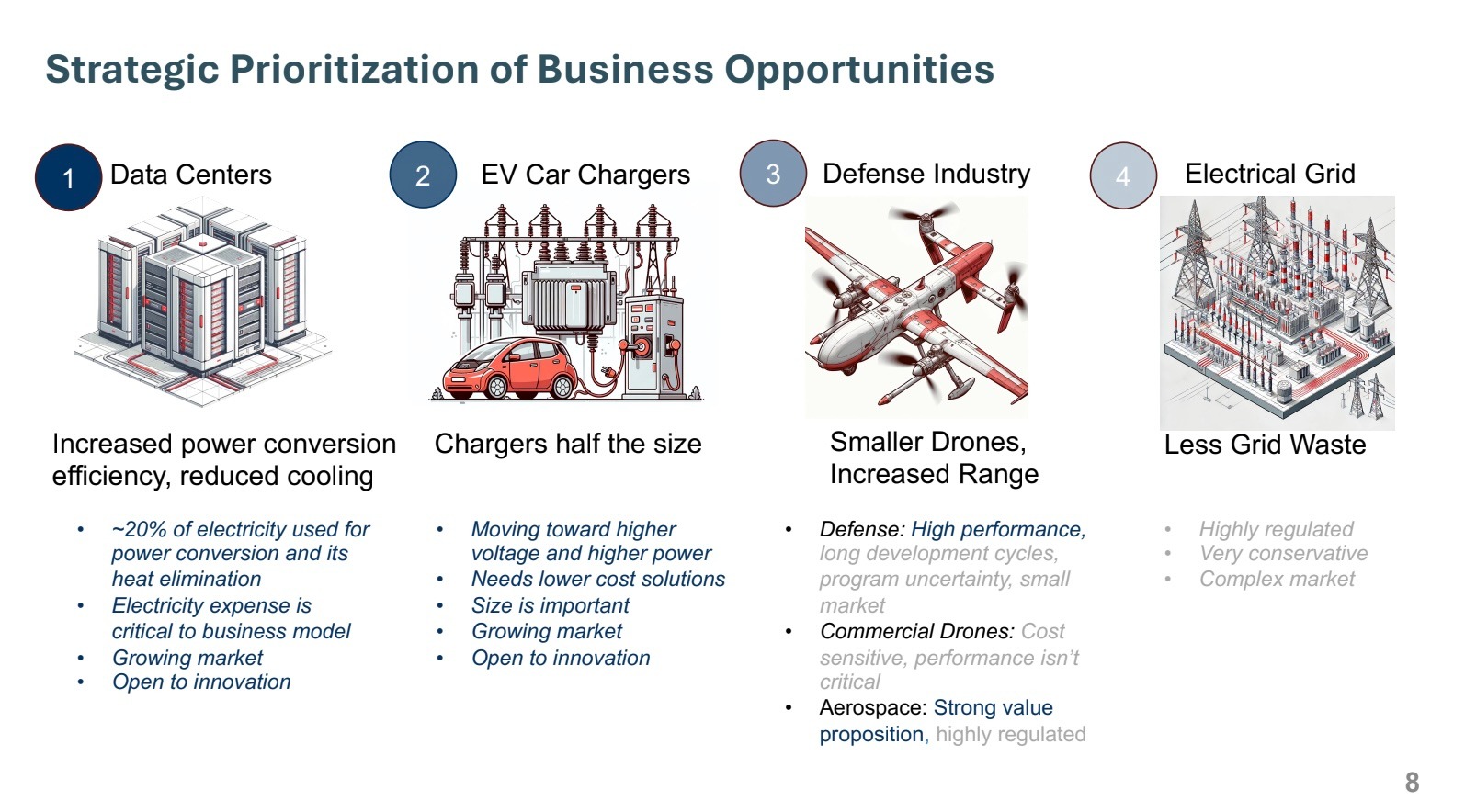

The best way to describe the problem your customers face is to start with a slide that outlines the general industry challenge that you are addressing. From here, the next slide should outline the specific problem your end customers face, and the direct business implications of it.

What gets VCs excited

- Problems where the economic pain is 10x the cost of the solution (e.g., data center spending $100M/year on power, your chip saves $50M)

- Demonstrable proof that customers have tried alternative solutions and failed (shows urgency and validates that incremental improvements don't work)

- Problems that are getting worse over time (end of Moore's Law scaling, increasing AI model sizes, growing edge compute demands)

- Clear evidence that customers are currently accepting expensive tradeoffs (buying 3x more chips to compensate, limiting deployments, delaying products)

Red flags

- "Nice to have" problems that customers aren't actively trying to solve with significant budget

- Problems that could be solved with software optimization, better cooling, or process improvements rather than new silicon

- Focusing on technology challenges ("transistor density is limited") rather than customer outcomes

- Generic statements about AI compute demand without specific customer validation or quantified pain

- Problems that only matter at hyperscale (signals your TAM may be just 10-20 companies)

Solution

Show why your solution is the best solution to this problem

Your solution slide should detail the precise benefits (by means of price or business outcomes delivered to your end customer) that show why you solve this problem for your customer.

Effective slides bridge the gap between technical architecture and business value. Rather than leading with transistor counts or die size, show how your chip's capabilities translate to customer ROI:

- Quantified performance metrics: "Achieves 3x inference throughput per watt versus H100 on transformer workloads" rather than "uses novel dataflow architecture". Claims here hold much higher weight when metrics are backed by 3rd party validation.

- Direct cost comparison: "Delivers equivalent compute at $0.15/inference vs. $0.45/inference on current solutions" with clear assumptions

- Operational improvements: "Reduces data center power consumption by 40% for equivalent workloads, saving $12M annually for a 50MW facility"

- Deployment characteristics: "Drop-in replacement for existing accelerator cards with standard PCIe interface, runs existing PyTorch models with our compiler"

For chips, the solution must address why your approach is better than: (1) waiting for the next generation from incumbents (Nvidia, Intel, AMD), (2) using existing chips with software optimization, (3) using FPGAs or other flexible solutions, and (4) competing startup approaches.

Your solution slide should demonstrate why you’re the best solution in light of current solutions, incumbents, and other potential entrants.

What gets VCs excited

- Clear TCO (total cost of ownership) advantage of 2x or greater with conservative assumptions

- Solutions that address multiple pain points simultaneously (e.g., improves performance, reduces power, and simplifies deployment)

- Evidence that your solution works on real customer workloads, not just synthetic benchmarks

- Demonstration of a software stack that makes the hardware accessible (compiler, drivers, framework integration)

- Solutions with clear upgrade paths (next-gen chips that build on the same architecture and software ecosystem)

Red flags

- Performance claims only on narrow benchmarks that don't reflect real workloads

- Leading with architecture diagrams and transistor specs before showing business value

- Comparing only to 2-3 year old incumbent products without addressing their roadmaps

- Claiming you can beat incumbents at everything—shows lack of focus on where you truly differentiate

- Missing software story ("customers will port their code")—in chips, the software ecosystem is often harder than the silicon

Technical Risk

How to convince investors to get behind the remaining technical risk that you have

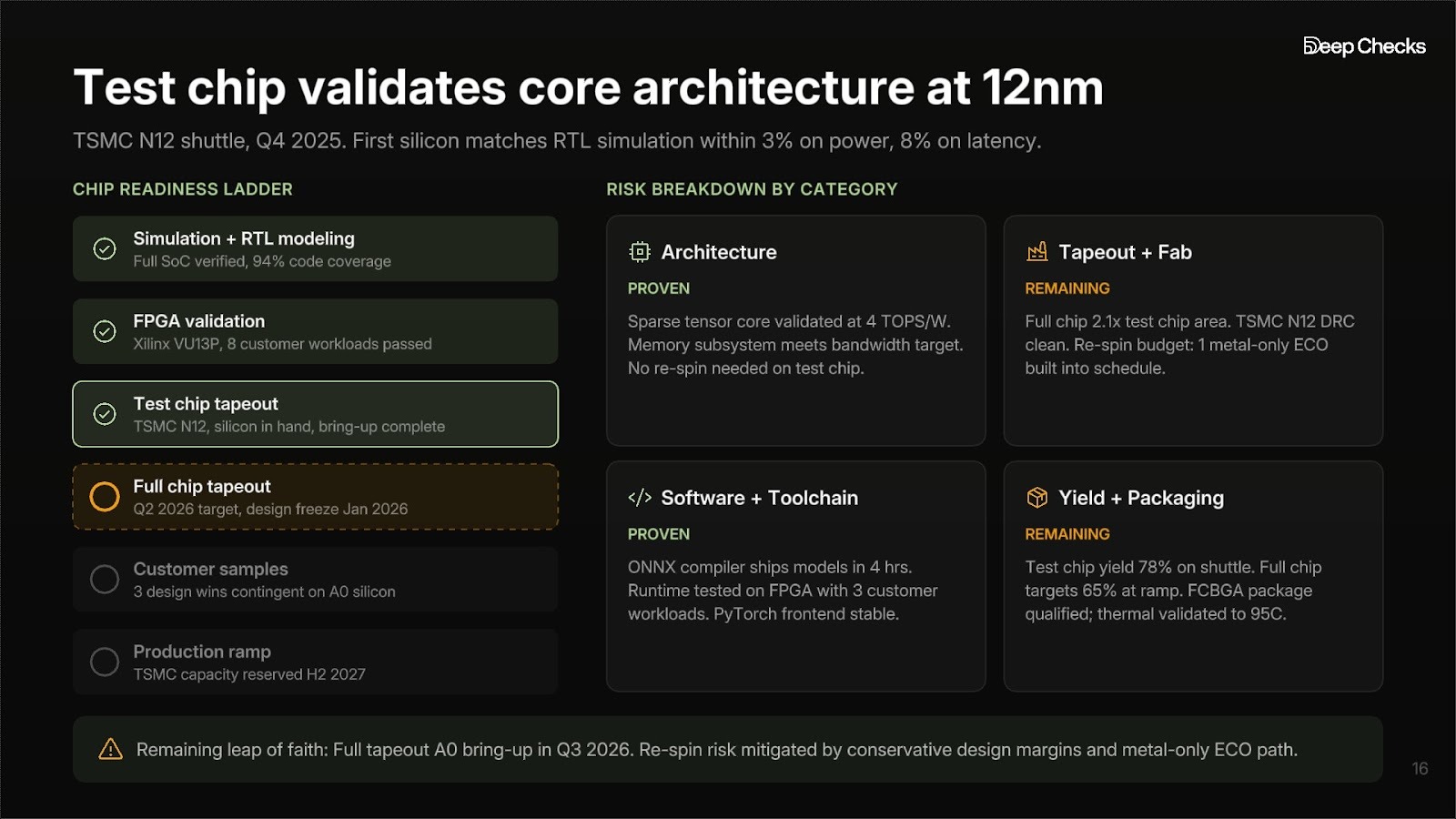

After your solution slide, investors will want to know what your technology is, what your unique insight to be able to build it was, and what its technical readiness level is. This slide should include technical diagrams, your TRL level, and highlight any remaining customer benefits not covered in the solution slide.

In showing this, keep in mind: Deeptech venture investors typically accept engineering risk (if your team can credibly tackle it and it's technically feasible) but not scientific risk (where your product might simply not work). Early stage VCs want to know:

- What has been proven

- What needs to be proven (within technical efficacy, system efficiency, technoeconomics, or scale-up)

- Why you're confident you'll achieve this (known engineering problems are far more credible than "it works in simulation but has never been fabricated")

Semiconductors generally have long development cycles, high NRE costs, and limited iteration opportunities. Investors evaluate risk across multiple dimensions:

- Architecture and design risk: Is the fundamental approach sound? Have you validated key design choices through FPGA prototyping, simulation, or prior tapeouts? Show your performance models and how they compare to actual silicon results from test chips.

- Tapeout and fabrication risk: What node are you targeting and do you have foundry relationships? Are you targeting a 2nm one where the tapeout requires you raising $100M+ minimum? Or a legacy node where you can prove value for much less? Have key team members done successful tapeouts at this node before? What's your plan for securing fab capacity in a supply-constrained environment?

- Software and toolchain risk: Hardware without software is useless. Can you show a working compiler, drivers, and framework integration? Have customers run their actual workloads, not just your internal benchmarks?

- Yield and manufacturing risk: Especially for advanced packaging (chiplets, 3D stacking), what are your yield assumptions? How do you plan to handle known-good-die testing? What's your path to volume production?

- IP and export risk: Do you have freedom to operate? Are there export control considerations? Have you secured necessary IP licenses (CPU cores, interface PHYs, etc.)?

Use a clear framework for communicating technical readiness: (1) Simulation/modeling complete, (2) FPGA validation, (3) Test chip tapeout, (4) Full chip tapeout, (5) Customer samples, (6) Production ramp. Be specific about where you are and what milestones unlock next-round funding.

Show you understand the difference between "works in simulation" and "works in silicon." Address: What's your plan if the first silicon has bugs? How many tapeout iterations are you budgeting for? What's your bring-up and debug strategy? What does your test coverage look like?

Your technical risk slide should demonstrate how far you’ve proven your chip, and what remaining steps there are in getting it to commercial readiness.

What gets VCs excited

- Successful test chips demonstrating key architectural innovations

- Clear delineation of what's proven vs. what needs engineering work, with credible timeline and team capability

- Proprietary technical insights that are hard to replicate (novel architecture, unique IP, or manufacturing innovations)

- Relationships with foundries that de-risk manufacturing

- Working software stack demonstrated with real customer workloads

Red flags

- "It works in simulation" without a pathway to silicon validation or FPGA proof points

- Reliance on unproven process technology or packaging approaches

- No discussion of what happens if first silicon doesn't meet specs

- Claiming a single tapeout will be production-ready (very rare in practice)

- Teams without prior tapeout experience trying to do leading-edge designs

- No clear path to securing foundry capacity or required IP licenses

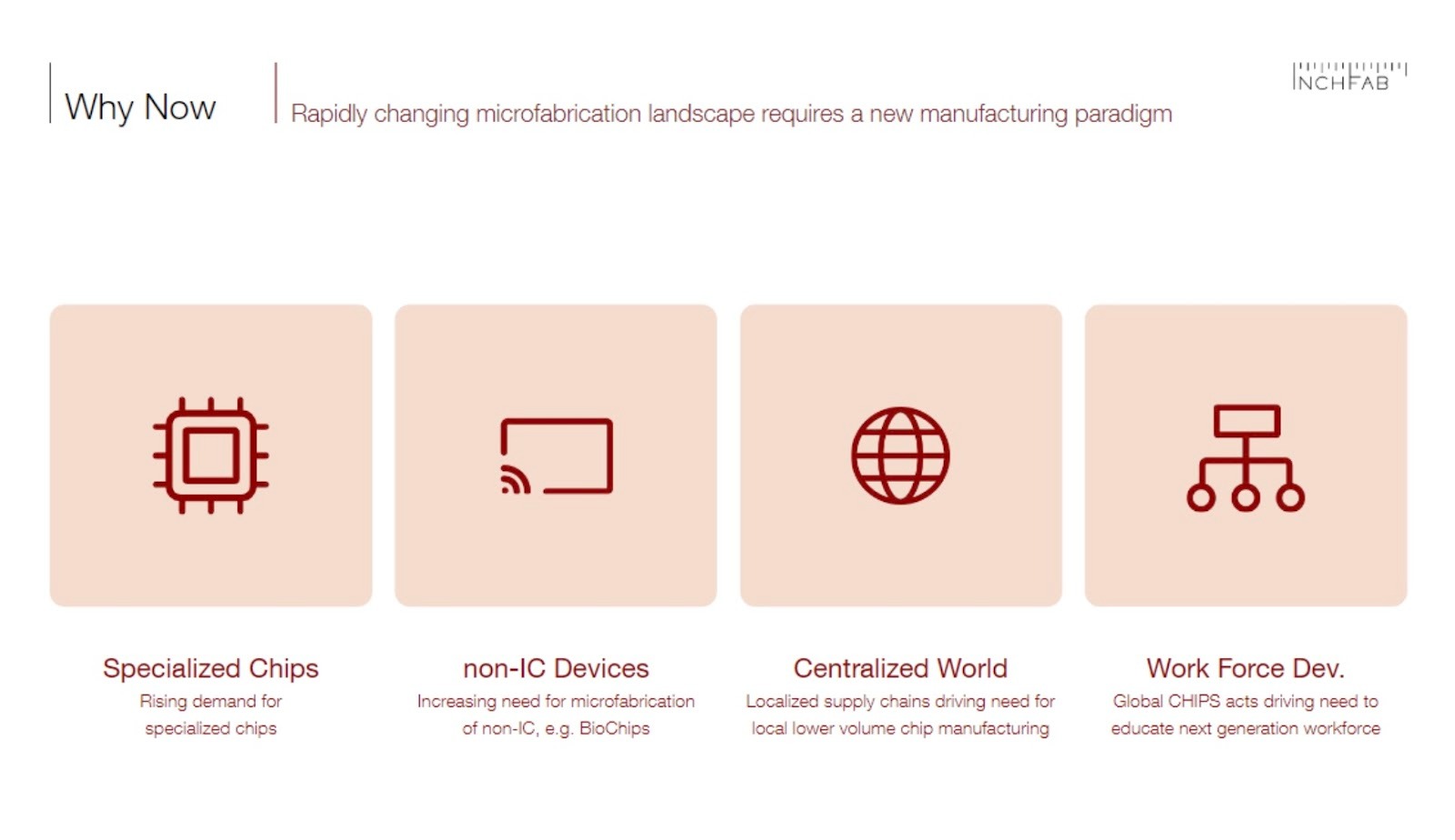

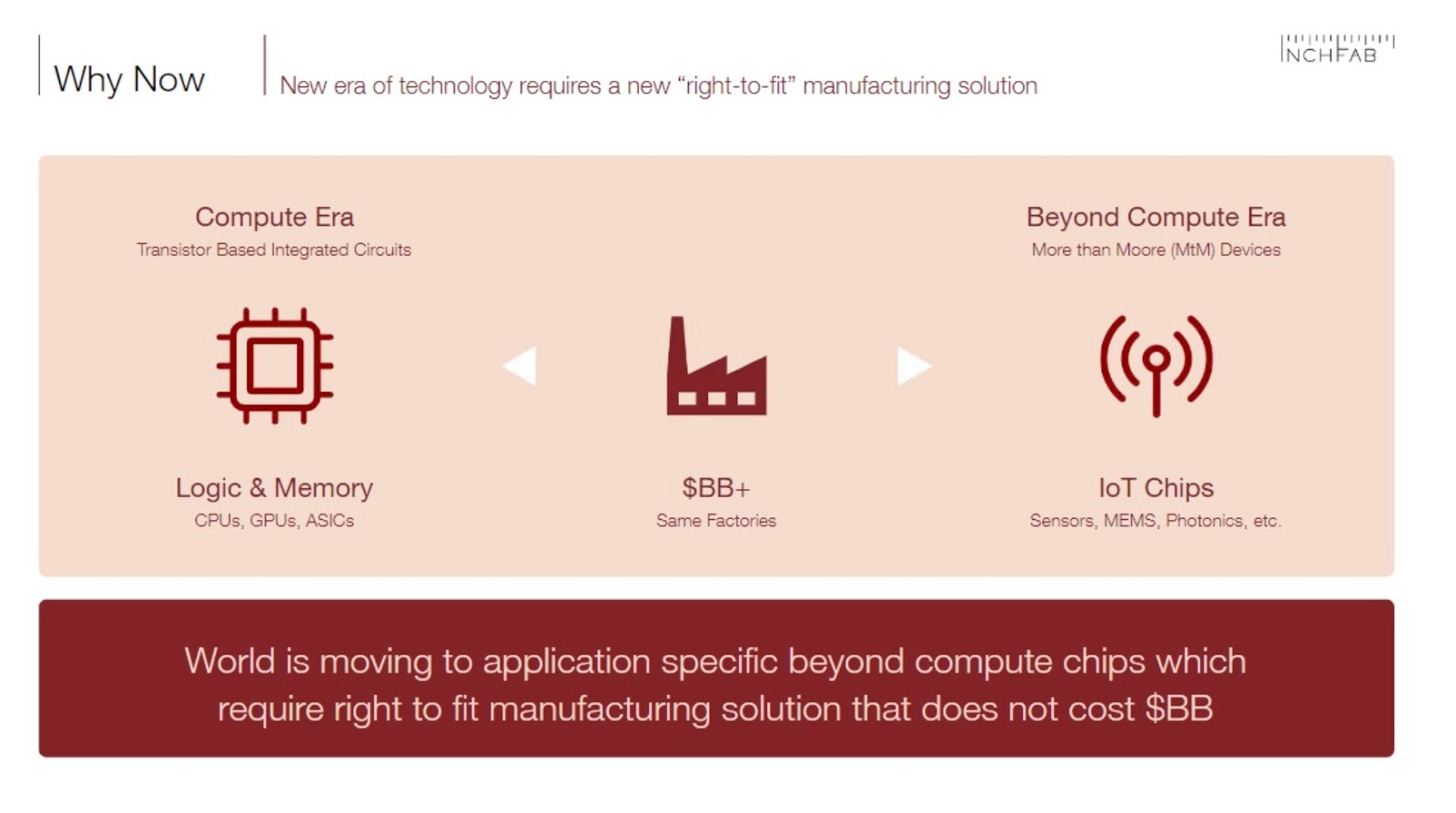

Why Now

Demonstrating why your startup has just become possible to build

Many times, ideas have been tried before and failed to materialize. By describing what has changed in the world that makes it uniquely possible to build your business today, investors gain confidence in your business.

Inflection points across technology, policy, consumer behavior, or buyer demand create compelling narratives to demonstrate this. Here are examples we're seeing in 2026:

Demand

- AI model sizes growing 10x annually, outpacing hardware performance improvements

- Hyperscalers designing custom silicon because merchant solutions can't meet their needs

- Edge AI deployments requiring 10-100x better efficiency than current solutions

Technology

- Chiplet and advanced packaging enabling disaggregated designs that reduce NRE

- RISC-V maturity eliminating CPU licensing barriers and enabling custom extensions

- Open-source frameworks (MLIR, LLVM, RISC-V toolchains) have dramatically reduced the effort to build competitive compilers and software stacks

Policy

- CHIPS Act funding enabling domestic manufacturing and R&D investment

- Export controls creating demand for non-China-dependent supply chains

- Sovereign wealth funds and government investors entering the semiconductor space

Market structure

- Nvidia's dominance creating urgency for alternatives among hyperscalers

- Fab capacity constraints making foundry relationships valuable assets

- TSMC, Samsung, and Intel are building new fabs in the U.S., Europe, and Japan. GlobalFoundries, UMC, and others are expanding mature node capacity.

The most credible "why now" arguments combine 2-3 of these factors. For example: "Transformer workload convergence gives us a stable optimization target, chiplet packaging lets us achieve competitive performance without leading-edge NRE, and CHIPS Act funding de-risks our domestic manufacturing strategy."

What gets VCs excited

- Specific, quantified changes in enabling technologies ("Chiplet packaging costs have dropped 60% in 3 years")

- Confluence of multiple trends making your solution newly viable (technology + policy + market demand)

- Evidence that customer urgency has shifted ("Hyperscalers who wouldn't take meetings 3 years ago are now proactively reaching out")

- Recent failures of alternative approaches that validate your different method

- Demonstration that you're uniquely positioned to capitalize on these trends due to team background or early insights

Red flags

- Generic claims about AI demand without showing what specifically changed

- Why now arguments based on hypothetical future improvements ("When 2nm becomes available...")

- Ignoring why previous similar startups failed (there have been many AI chip companies)

- Claiming your technology breakthrough is the "why now" (that's technical risk, not market timing)

- AI demand arguments without acknowledging that chip companies have always claimed growing compute demand as "why now"

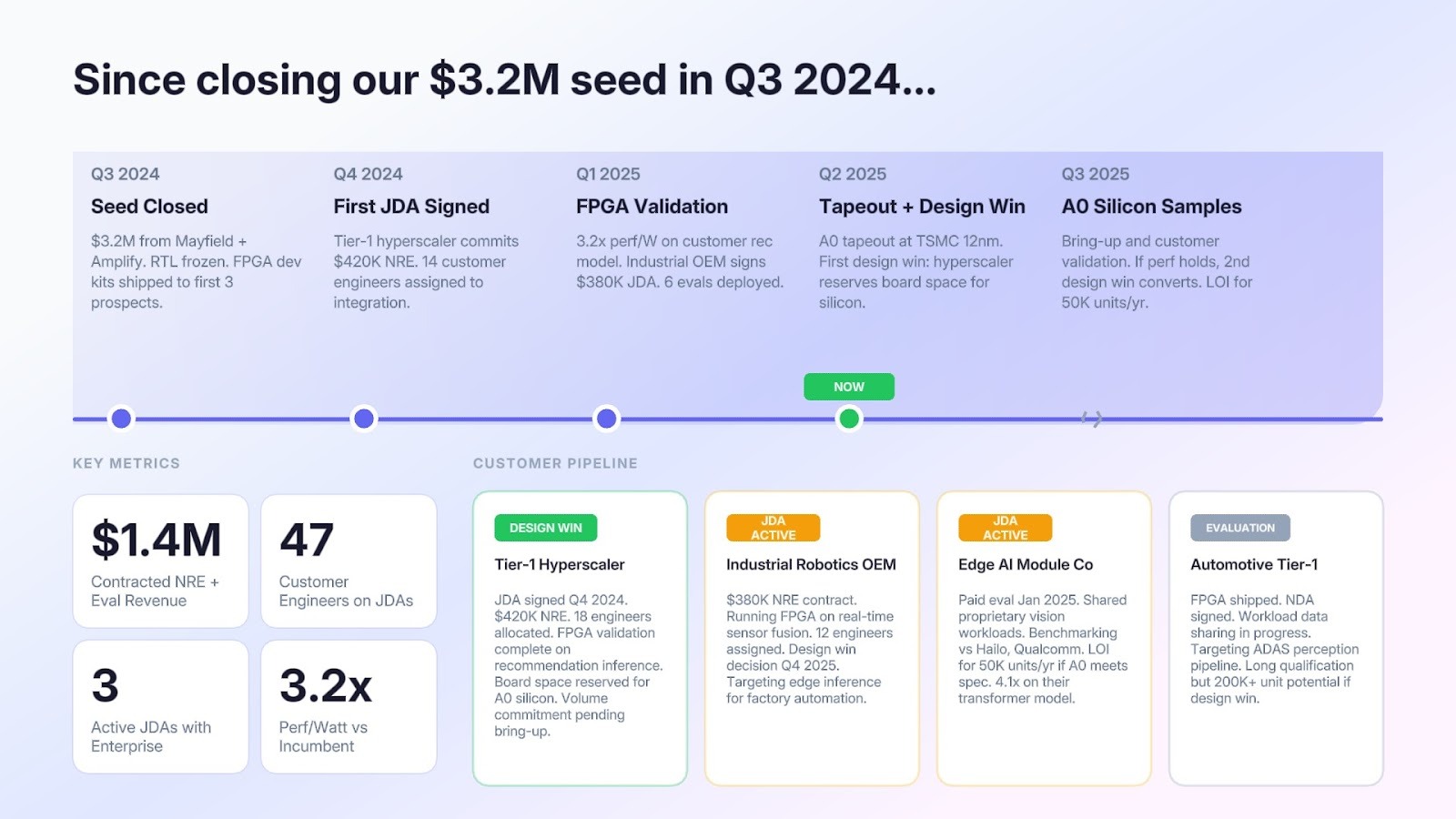

Traction

How to show there's demand for your product before the market has adopted it

In order of least to most convincing, there are three ways you can demonstrate your traction to VCs:

- Design wins (most valuable): Customers who have committed to using your chip in their products. For chips, this often means they've allocated board space, started software integration, or signed development agreements. Critical questions: Have they assigned engineering resources? Are they paying for early access? Have they committed volumes?

- Joint development agreements (JDAs): Customer co-development where they're investing resources (engineering time, sharing specifications, providing feedback on architecture). Show their skin in the game—are they assigning engineers? Sharing proprietary workload data? Committing to evaluation timelines?

- Letters of intent (LOIs): For semiconductors, LOIs must include specific conditions and volumes. "Will purchase 100K units annually upon achievement of specified performance at $X price point" is strong. "Interested in evaluating" is worthless. Include contingencies explicitly.

- Technical validation: Customers running their actual workloads on your FPGA prototypes, test chips, or simulators. Show concrete results: "Customer X achieved 2.3x throughput on their production inference workload."

- Customer discovery depth: For pre-silicon companies, show 50+ customer conversations across target segments. Document specific requirements, willingness-to-pay, evaluation criteria, competitive alternatives they're using. Include details like: Who's the decision-maker? What's their qualification process? What performance/cost threshold triggers adoption?

For chip companies raising a seed, you typically need deep customer validation and a path to technical proof points (FPGA, simulation, test chip). Your traction slide should show how far along these axes you are.

What gets VCs excited

- Design wins with tier-1 customers (hyperscalers, major OEMs) who have technical credibility

- Customers paying for early access, engineering samples, or development agreements

- Evidence of land-and-expand potential: customers starting with evaluation quantities but planning significant volume

- Multiple design wins across different customer segments showing the solution works broadly

- Customer champions willing to speak with investors and provide technical validation

- Inbound interest from customers who discovered you organically (shows market pull)

Red flags

- Only internal benchmarks without customer workload validation

- LOIs without specific performance requirements, volumes, or pricing

- All traction with a single customer (high concentration risk and signals possible custom design)

- Customer interest but no one willing to speak with investors or provide references

- Design wins contingent on performance levels you haven't demonstrated

- Long evaluation cycles (2+ years) without interim proof points or payments

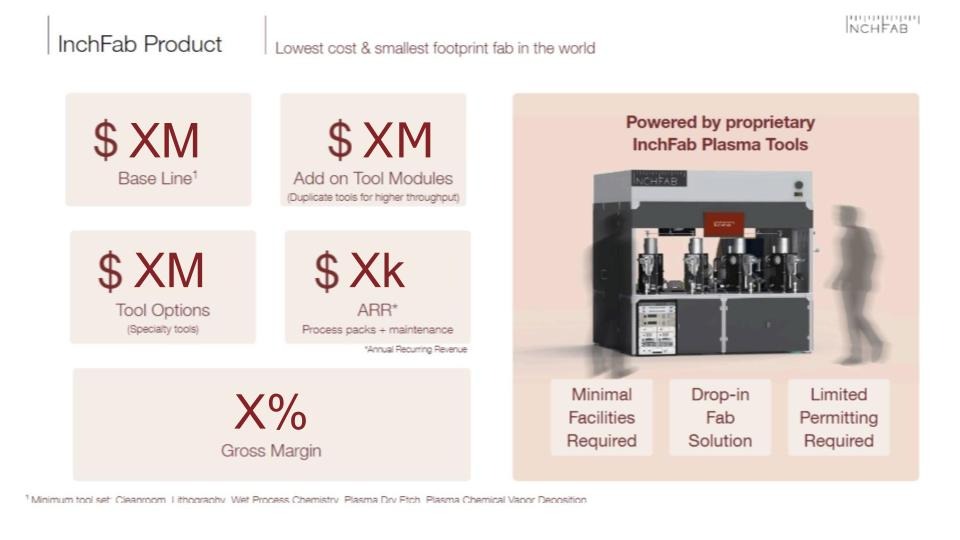

Business Model

How VCs think about your economics

Your business model slide should include the basics of how you make money, the high level economics of price point to end customers, and margin you are able to achieve yourself.

VCs evaluate chip economics across several dimensions:

Revenue model options

- Chip sales (product): Customer buys chips outright. Typical gross margins 50-70% at scale for differentiated products. Advantage: simpler sales motion, customers understand it. Disadvantage: lumpy revenue, customer controls deployment.

- Silicon-as-a-Service: Customer pays based on usage (per inference, per query, per compute hour). Emerging model for cloud deployments. Creates recurring revenue and aligns pricing with value. Requires significant deployment infrastructure.

- IP/licensing: License your design to others to incorporate into their chips. Lower revenue per customer but capital-light with high margins. Works best for foundational technology (interfaces, cores, accelerator blocks).

- Systems/solutions: Sell complete accelerator cards, servers, or appliances. Higher ASPs but more complex operations and support. Often necessary for AI/HPC applications where customers want turnkey solutions.

Critical unit economics to show

- Die cost and COGS: Cost to manufacture one chip at current and projected volumes. Include wafer cost, yield assumptions, packaging, testing. Show path from early production (often 20-40% gross margin) to scale (target 50-70%).

- NRE and tapeout costs: Non-recurring engineering for each chip generation. Show how your approach manages NRE (chiplets, mature nodes, design reuse).

- ASP and volume assumptions: What's your average selling price and how does it compare to incumbent solutions? What volumes are needed to achieve target margins? How does ASP evolve as you scale?

- Software and support costs: Ongoing investment in compilers, drivers, frameworks, and customer support. In chips, software teams are often as large as hardware teams. Show how these costs scale (or don't) with customer count.

The most important semiconductor business model metric is gross margin trajectory and path to profitability. Fabless chip companies should target 50%+ gross margin at scale. Show your assumptions clearly: wafer cost per mm², yield at production volumes, packaging cost, test cost.

Your business model should detail these by means of sale price to your end customer and margins you’re able to achieve.

What gets VCs excited

- Clear path to 50%+ gross margins at scale with supporting cost breakdown

- Evidence of pricing power (customers willing to pay premium for differentiated performance)

- NRE strategy that manages risk (chiplets, mature nodes, design reuse across generations)

- Software/platform revenue that creates stickiness and recurring revenue alongside chip sales

- Land-and-expand dynamics where initial design wins lead to 10x+ volume expansion

- Clear understanding of volume thresholds needed for different margin levels

Red flags

- Gross margins below 40% even at scale (suggests commodity positioning)

- Unrealistic yield assumptions (especially for new packaging technologies or advanced nodes)

- NRE assumptions that don't account for multiple tapeout iterations

- Pricing based on performance comparisons that customers won't pay for. Overemphazising buyer willingness to pay in light of hyperscaler spend has become quite common.

- Software costs not included in operating model

- Business model assumes very high volumes without evidence of market demand at those levels

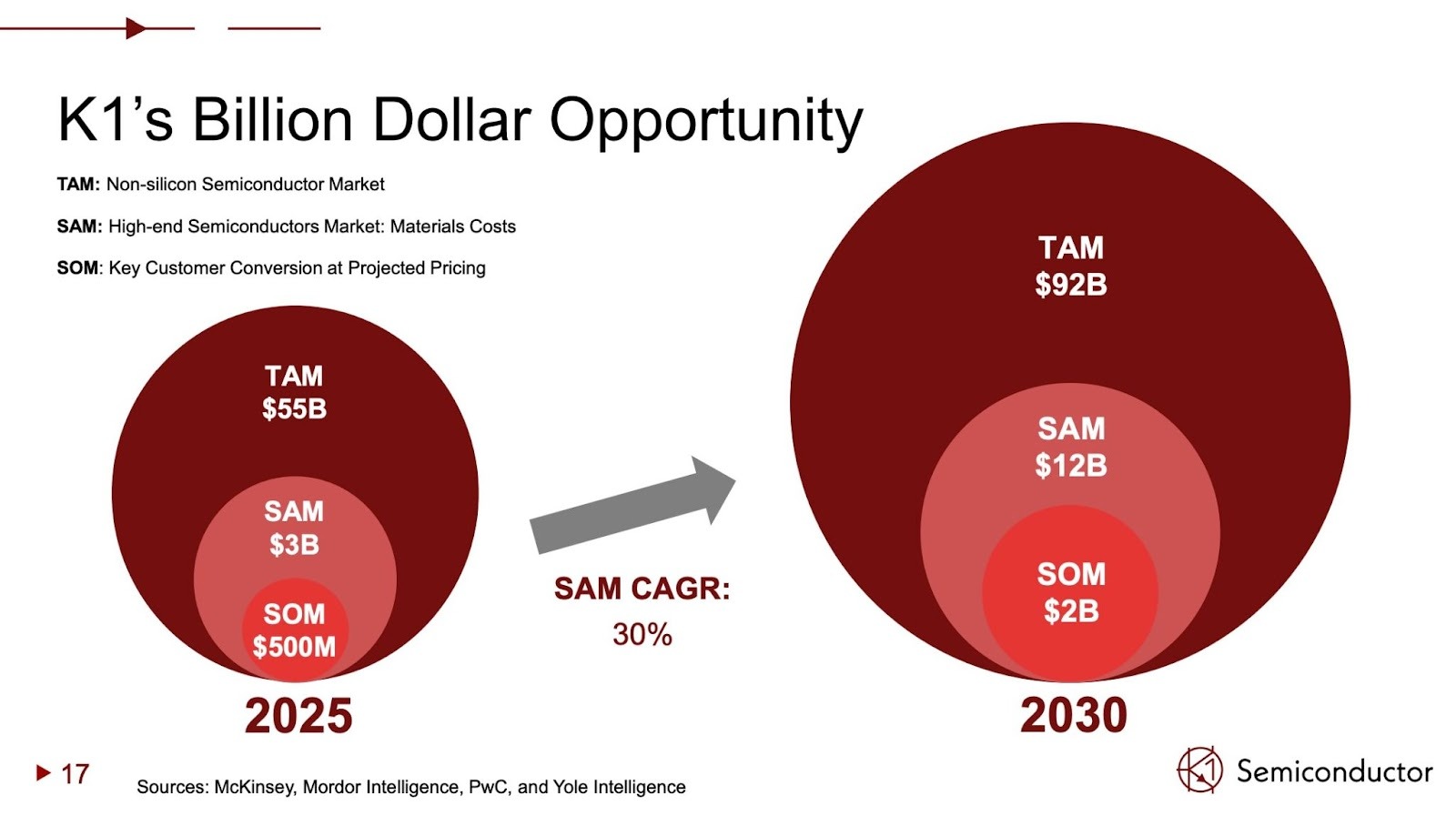

Market Size

Why bottom up beats top down

Your market sizing slide should be broken down into your:

Total addressable market: The total market size your business could theoretically capture.

Serviceable addressable market: The portion of the TAM you could realistically capture with your business model, technology, and resources.

Serviceable obtainable market: The portion of the SAM you are targeting in the short term.

In building your bottom up market sizing, consider:

SAM requires technical constraints: Your chip has technical limitations—it targets specific workloads, power envelopes, and price points. Be explicit about what percentage of the TAM you can technically address. (e.g., "Our architecture excels at batch inference but isn't optimal for real-time serving, representing 40% of inference compute")

SOM is about go-to-market focus: Which customer segments are you targeting first? Why? How big is just that segment? (e.g., "Initial focus on cloud AI inference in North America—representing 15 hyperscaler and major cloud customers, $2B opportunity")

It’s acceptable to lean towards top down if bottom up is hard to quantify, and it is ok to use projections for market size so long as it’s clear how you’re arriving at your conclusions (ie TAM is based on 2030 estimates).

A bottom-up market sizing for SOM and SAM backed by customer input on pricing lends to the greatest degree of credibility.

What gets VCs excited

- TAM >$5B with clear, defensible bottom-up math (shows venture scale opportunity)

- SOM that's achievable in 3-5 years and represents a $100M+ revenue opportunity on its own

- Market sizing validated by customer conversations ("talked to 10 hyperscalers, average need is 50K units/year")

- Evidence of market growth—workload compute requirements increasing faster than incumbent hardware improvements

- Platform potential where initial application opens adjacent markets (with a realistic expansion path)

Red flags

- Top-down market sizing only ("$100B AI chip market, we'll capture 1%")

- TAM calculated by multiplying all AI training/inference compute by price per chip (ignores that most workloads run fine on GPUs)

- Market size claims that don't match customer discussions (claim millions of chips when customers say 10K-50K)

- Assuming 100% workload match or ignoring incumbent solutions ("all AI will move to our architecture")

- Adding multiple disconnected markets without explaining how you'll actually serve them all (data center + automotive + edge + IoT)

Go to Market

Showing you can become big enough, fast enough

This slide should outline who your customers will be, how you reach them, and how you will stage your GTM if your customer type changes with scale. Within the pitch, the most important question to answer is how your GTM motion can support a venture scale amount of revenue (usually $100M+) within the decade timeframe of a venture fund. VCs will generally use this slide to understand your depth of knowledge on the sales cycle as well.

Unique to semiconductors, GTM includes long design cycles (18-36 months from evaluation to production), high switching costs, and technically sophisticated buyers. Your GTM slide must address:

Customer segmentation and sequencing

- Initial beachhead: Start with a specific customer segment willing to evaluate new silicon. Often: (1) hyperscalers with engineering capacity and urgency to differentiate, (2) tier-2 cloud providers, (3) vertically integrated companies (automotive, telecom) with clear workload requirements.

- Expansion path: How do you move from early adopters to the mainstream market? What changes—product maturity, software ecosystem, support capabilities?

- Enterprise timing: Large enterprises won't evaluate unproven silicon but represent massive scale opportunity once you have credibility and ecosystem support.

Your GTM slide should show who you target at each stage of the company, and VCs will use it to probe your knowledge of the sale process to your end customers.

What gets VCs excited

- Clear beachhead with proof of repeatable evaluation motion (completed 3+ technical evaluations with similar customers)

- High evaluation-to-design-win conversion rates showing product meets customer needs

- Land-and-expand evidence where initial deployments expand within customers

- Strategic partnerships with server OEMs, cloud providers, or system integrators

- Customer references willing to speak publicly about adoption and results

Red flags

- Assuming short design cycles (6-12 months) without evidence

- "We'll sell to everyone with AI workloads" without clear segmentation

- Evaluations that don't convert to design wins (suggests product or software gaps)

- Reliance on channel partners without proof of direct customer traction first

- No clear path to $100M revenue or math requiring implausible customer counts

- No plan for building the software ecosystem and developer relations function

Competition

As markets become crowded, how to create defensibility

The strongest defensibility arguments show your solution is directionally impossible or highly unlikely for top incumbents to build themselves. It should be technically novel, challenging to replicate without your team's specific expertise, and protected by IP. Over time, becoming a trusted industry leader and achieving economies of scale creates durable advantages over future competitors.

Semiconductor competition is multi-dimensional because you're competing against: (1) incumbent chip vendors (Nvidia, Intel, AMD, Qualcomm), (2) hyperscaler custom silicon (Google TPU, Amazon Trainium, Microsoft Maia), (3) other chip startups, and (4) customers sticking with general-purpose solutions (GPUs, CPUs). Your competitive positioning must address all four:

Common competitive axes for chips:

- Performance vs. Efficiency: Absolute performance (throughput, latency) vs. efficiency (perf/watt, perf/$). Where do you optimize? Different customers care about different axes.

- Specialization vs. Flexibility: Highly optimized for specific workloads vs. programmable for broader use cases. Trade-offs in performance, software investment, and market breadth.

- Software Ecosystem vs. Hardware Performance: Nvidia's CUDA moat shows that software often matters more than hardware specs. How does your software story compare?

- Time-to-Market vs. Leading Edge: Can you ship sooner on mature process nodes vs. waiting for leading-edge capacity? Different strategies for different market windows.

Addressing incumbent risk:

VCs will ask: "Why won't Nvidia/Intel/AMD build this? Why won't Google/Amazon/Microsoft use their own silicon?" Your answer must show:

- Technical approach fundamentally different from incumbent architectures (not just incremental improvement)

- Market segment too specialized for broad-market incumbents to prioritize (they optimize for volume)

- Hyperscaler custom silicon only serves their own needs, creating opportunity for merchant solutions

- Speed and focus advantages (you can iterate faster on specialized workloads than large incumbents)

Tied to your competitive positioning, is how you maintain defensibility over time:

Semiconductor-specific defensibility

- Architecture and IP: Novel architecture with patent protection that creates fundamental performance or efficiency advantages. Must be meaningful—not just "different" but demonstrably better on metrics customers care about.

- Software moat: Compiler, libraries, framework integration, and developer tools that make it easy to use your hardware. Every customer deployment deepens the software ecosystem advantage. This is often the most durable competitive advantage in chips.

- Customer deployment and data: Production deployments generate optimization insights and customer relationships that are hard to replicate. First customer to deploy at scale has significant advantages in learning and iteration.

- Manufacturing relationships: In a capacity-constrained environment, foundry relationships and packaging partnerships become strategic assets. Locked-in capacity at TSMC or advanced packaging partners is increasingly valuable.

Your competition slide should detail how you beat incumbents and other potential emerging technologies.

What gets VCs excited

- Unique technical approach with strong IP protection (patents filed/granted on core architecture)

- Demonstrable performance advantages (2x+ better on key metrics) validated by customer benchmarks

- Software ecosystem showing early traction (developer adoption, framework integration, customer tools)

- Strong head start (18+ months lead on closest competitor) with proof they can't catch up easily

- Market positioning that makes you the clear choice for a specific segment ("the inference chip for recommendation systems")

- Customer validation that your differentiators matter ("chose us over Nvidia because of Y")

Red flags

- "No competitors" or "we're the only ones doing X" (shows lack of market research)

- Competitive axes that don't drive purchase decisions ("we use a different instruction set" when customers care about TCO)

- No clear answer to why Nvidia with $50B R&D budget won't simply build your approach

- Differentiation only in hardware specs, ignoring software ecosystem reality

- Claiming patent protection on obvious approaches or easily-worked-around innovations

- Multiple well-funded competitors further ahead with similar approaches (suggests you're late to a crowded market)

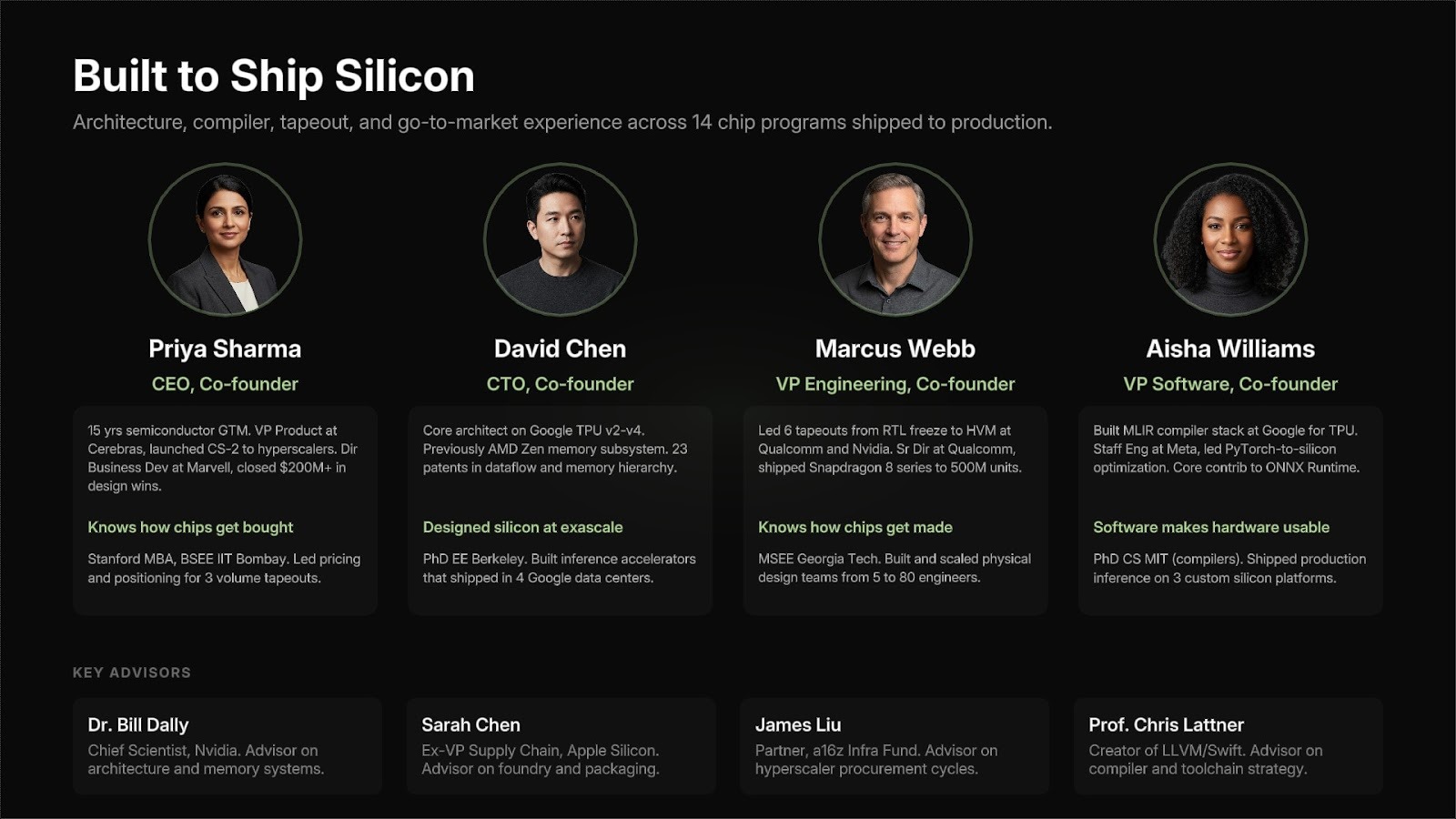

Team

What makes for a world-class founding team?

At Julian Capital, we’ve written about what makes a great founding team here. We're excited by founding teams who are:

- Commercially minded with technical depth

- Building their life's work—the culmination of their career or their final pursuit

- Ambitious enough to scale to $1B+ valuation

- Relentlessly resourceful with high agency

- Persuasive and authentic storytellers

- Comprehensive in thinking through all business avenues (GTM, competitive landscape, bottom-up TAM, etc)

Semiconductors require an unusually deep and specialized skill set because you're developing complex silicon, building software ecosystems, and selling into enterprise customers. The strongest chips founding teams combine:

- Deep architecture expertise: At least one founder who has designed production chips—ideally as lead architect or technical leader at a successful semiconductor company. They need to understand microarchitecture, memory systems, interconnects, and system-level tradeoffs deeply enough to make hard decisions under uncertainty.

- Software and compiler expertise: Hardware without software is useless. Someone who understands compilers, frameworks, and what it takes to build a usable software stack. Many chip startups fail because they underestimate software—it's often 50%+ of the engineering effort.

- Tapeout and productization experience: Someone who has taken chips from design through tapeout to production. Understands: design verification, physical design, foundry relationships, packaging, testing, yield engineering. Without this, teams massively underestimate the path to working silicon.

- Customer and market knowledge: Deep understanding of target customer needs, buying processes, and what actually drives purchasing decisions. Ideally someone from the customer side who knows what features matter, what the competitive alternatives look like, and how to navigate enterprise technical sales.

You certainly don’t need all of this expertise in a founding team, but a slide that demonstrates what you do bring to the table helps build investor confidence.

What gets VCs excited

- Teams that combine deep technical expertise with commercial orientation and customer relationships

- Founders who have successfully shipped production chips before

- Software expertise prominently represented

- Clear roles and decision-making structure among co-founders

- Mission-driven founders committed for the long-term

- Demonstrated ability to navigate ambiguity and make hard tradeoffs

Red flags

- All-academic teams with no industry or product experience

- Teams without anyone who has completed production tapeouts

- Hardware-only teams with no software/compiler expertise

- Founders who can't articulate clear division of responsibilities or have overlapping roles

- Teams that can't recruit strong engineers

- Lack of urgency or treating this as a research project rather than a business

The Ask: Use of proceeds and round size

The ask shows how much you are raising and what you plan to accomplish with it. We wrote about choosing how much to raise here.

Semiconductor startups face some of the highest capital requirements of any hardware category, and the gap between a working chip and a revenue-generating product is measured in years and tens of millions of dollars. Your use of funds should be tied to a specific tape-out, process node milestone, or customer qualification event, and your use of proceeds must reflect the actual cost structure of the semiconductor development cycle.

Be precise about where you are in the chip development cycle and what this round funds. "This $6M seed funds our first full tape-out on TSMC's 28nm process, evaluation silicon to three anchor customers, and applications engineering support to reach design-win status." Your ask slide should work back from the specific commercial, technical, and manufacturing milestones you aim to achieve with it.

What gets VCs excited

- Raise tied to a specific tape-out or process milestone, with a realistic budget that includes re-spin contingency

- Design-win pipeline with anchor customers willing to co-fund development or commit to volume

- Fabless model with identified foundry partners that allows capital efficiency relative to IDM alternatives

- IP strategy: patents on architecture, process, or design that create licensing potential alongside product revenue

- Non-dilutive funding: DARPA, CHIPS Act programs, state-level semiconductor incentives

Red flags

- Tape-out budget with no re-spin contingency—first silicon rarely works as expected

- No anchor customer or design-win pipeline—chips without committed end applications are very high risk

- Underestimating the cost and timeline of packaging, testing, and customer qualification

- Assuming leading-edge node access without confirmed foundry capacity—this is genuinely constrained

- Round sized insufficient to reach working silicon, leaving the company in a gap before it can raise again

Pitching: Do's & Don'ts

Here's how (and how not) to pitch:

The best pitches are conversational. Answers should be succinct yet demonstrate depth of thought. Great founders bridge vision with detail. They intimately understand their problem space and can explain it clearly—both the problem and the system around it. They understand the path to scale and can map how the business will evolve getting there.

Do:

- Lead with the customer problem, not your architecture: Start with "Hyperscalers spend $500M annually on inference compute that could be 3x more efficient" not "We built a novel dataflow accelerator." VCs invest in solutions to problems, not cool technology.

- Show working silicon or concrete prototypes: FPGA demos, test chip results, or simulation data on real workloads is worth 10 slides of architecture diagrams. Even better: customer workload results.

- Be honest about what doesn't work yet: VCs appreciate realism. "Our current prototype achieves 2x efficiency on attention layers; we need 3x for compelling TCO" builds more credibility than claiming perfection.

- Have crisp answers on unit economics and path to production: You should be able to discuss die cost, yield assumptions, NRE budget, and path to gross margin from memory.

- Demonstrate customer intimacy: Drop specific details that show you deeply understand your customer: "The ML platform team evaluates new hardware quarterly; their main gate is showing 2x TCO improvement on their production recommendation model."

- Address the software story upfront: Don't wait for VCs to ask "How do customers use this?" Proactively explain your compiler strategy, framework integration, and developer experience.

- Acknowledge and address incumbent risk: Don't wait for VCs to ask "Why won't Nvidia build this?" Address it upfront with a credible answer about focus, speed, or architectural advantages.

- Bring customer references: Offer to connect VCs with customers who will validate your technical approach and the problem you're solving. This accelerates due diligence dramatically.

Don’t:

- Get lost in architecture details: VCs don't need to understand your memory hierarchy or instruction set unless they ask. Focus on what the chip does and why it matters to customers.

- Oversell with cherry-picked benchmarks: A single great result on a narrow workload isn't convincing. Show performance across diverse workloads or explain why your target is narrow.

- Claim you'll beat Nvidia at everything: Every chip has tradeoffs. Be specific about where you win and where Nvidia (or other competitors) might be better for different use cases. Overpromising destroys credibility.

- Dismiss the software challenge: Saying "CUDA took years to build but our compiler will be ready at launch" shows you don't understand the software challenge. Be realistic about the investment required.

- Rely on unvalidated assumptions: If you haven't benchmarked on customer workloads, don't claim "customers will see 3x improvement." Better to say "need to validate on production workloads" than make up numbers.

- Ignore the path to production: If you've never done a tapeout, acknowledge this as a risk and show your plan to address it (hiring experienced talent, foundry partnerships, advisors).

Common traps chip founders fall into:

- Architecture-first framing: Leading with "we use a novel dataflow architecture" instead of "we solve the $10B inference efficiency problem."

- Unrealistic timelines: Claiming you'll go from design start to production silicon in 18 months when typical cycles are 3-4 years.

- Ignoring software investment: Focusing only on chip design while handwaving compiler and software stack.

- Overestimating adoption rates: Assuming 50% market penetration when new architectures typically achieve 10-20% even when clearly superior. Switching costs are real.

- Missing the forest for the trees: Getting stuck on detailed technical questions and losing sight of the big picture: Are you building a venture-scale business? Can you get to $100M revenue? Why will you win this market?

We hope this guide was useful to you! If you'd like to get in touch, don't hesitate to reach out to Julian.Capital or Intel Capital, and apply in <1 minute to get put in touch with thesis fit investors for free at DeepChecks.VC.